# **Realm Management Monitor**

**TF-RMM Contributors**

# **CONTENTS**

| 1   | About                  | 1  |

|-----|------------------------|----|

| 2   | Getting Started Guides | 11 |

| 3   | Process                | 21 |

| 4   | Design                 | 35 |

| 5   | Security               | 57 |

| 6   | Resources              | 77 |

| 7   | Glossary               | 81 |

| Bil | bliography             | 83 |

| Ind | dex                    | 85 |

**CHAPTER**

ONE

# **ABOUT**

### 1.1 Readme for TF-RMM

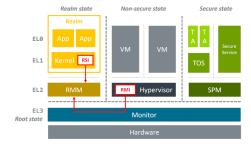

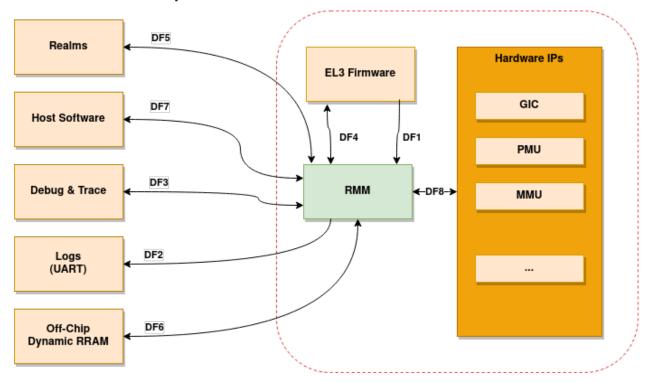

TF-RMM (or simply RMM) is the Trusted Firmware Implementation of the Realm Management Monitor (RMM) Specification. The RMM is a software component that runs at Realm EL2 and forms part of a system which implements the Arm Confidential Compute Architecture (Arm CCA). Arm CCA is an architecture which provides Protected Execution Environments called Realms.

Prior to Arm CCA, virtual machines have to trust hypervisors that manage them and a resource that is managed by the hypervisor is also accessible by it. Exploits against the hypervisors can leak confidential data held in the virtual machines. Arm CCA introduces a new confidential compute environment called a *Realm*. Any code or data belonging to a *Realm*, whether in memory or in registers, cannot be accessed or modified by the hypervisor. This means that the Realm owner does not need to trust the hypervisor that manages the resources used by the Realm.

The Realm VM is initiated and controlled by the Normal world Hypervisor. To allow the isolated execution of the Realm VM, a new component called the Realm Management Monitor (RMM) is introduced, executing at R\_EL2. The hypervisor interacts with the RMM via Realm Management Interface (RMI) to manage the Realm VM. Policy decisions, such as which Realm to run or what memory to be delegated to the Realm are made by the hypervisor and communicated via the RMI. The RMM also provides services to the Realm via the Realm Service Interface (RSI). These services include cryptographic services and attestation. The Realm initial state can be measured and an attestation report, which also includes platform attestation, can be requested via RSI. The RSI is also the channel for memory management requests from the Realm VM to the RMM.

The following diagram shows the complete Arm CCA software stack running a confidential Realm VM:

Figure 1. Realm VM execution

The TF-RMM interacts with the Root EL3 Firmware via the RMM-EL3 Communication Interface and this is implemented by the reference EL3 Firmware implementation TF-A.

More details about the RMM and how it fits in the Software Stack can be found in Arm CCA Software Stack Guide.

The Change-log and Release notes has the details of features implemented by this version of TF-RMM and lists any known issues.

#### 1.1.1 License

Unless specifically indicated otherwise in a file, TF-RMM files are provided under the BSD-3-Clause License. For contributions, please see License and Copyright for Contributions.

### **Third Party Projects**

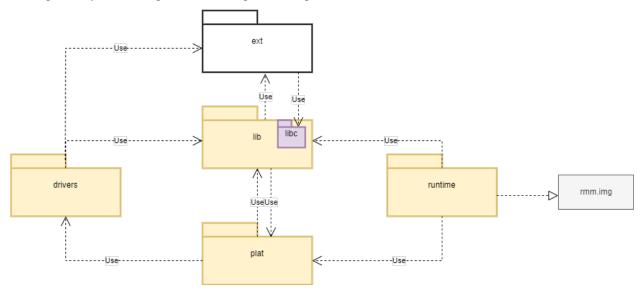

The TF-RMM project requires to be linked with certain other 3rd party projects and they are to be cloned from their repositories into ext folder before building. The projects are MbedTLS, t\_cose, QCBOR and CppUTest.

The project also contains files which are imported from other projects into the source tree and may have a different license. Such files with different licenses are listed in the table below. This table is used by the checkspdx tool in the project to verify license headers.

| File                             | License      |

|----------------------------------|--------------|

| lib/libc/src/printf.c            | MIT          |

| lib/libc/include/stdio.h         | MIT          |

| lib/libc/src/strlcpy.c           | ISC          |

| lib/libc/src/strnlen.c           | BSD-2-Clause |

| lib/allocator/src/memory_alloc.c | Apache-2.0   |

Table 1: List of files with different license

# 1.1.2 Contributing

We gratefully accept bug reports and contributions from the community. Please see the Contributor's Guide for details on how to do this.

# 1.1.3 Feedback and support

Feedback is requested via email to: tf-rmm@lists.trustedfirmware.org.

To report a bug, please file an issue on Github

# 1.2 Project Maintenance

Realm Management Monitor (RMM) is an open governance community project. All contributions are ultimately merged by the maintainers listed below. Technical ownership of most parts of the codebase falls on the code owners listed below. An acknowledgement from these code owners is required before the maintainers merge a contribution.

More details may be found in the Project Maintenance Process document.

2 Chapter 1. About

### 1.2.1 Maintainers

#### Mail

Alexei Fedorov < Alexei.Fedorov@arm.com>

#### GitHub ID

AlexeiFedorov

#### Mail

Arunachalam Ganapathy <arunachalam.ganapathy@arm.com>

#### GitHub ID

arugan02

#### Mail

Dan Handley <an.handley@arm.com>

#### GitHub ID

danh-arm

#### Mail

Javier Almansa Sobrino <javier.almansasobrino@arm.com>

#### GitHub ID

javier-almansasobrino

#### Mail

Mate Toth-Pal <mate.toth-pal@arm.com>

#### GitHub ID

Máté Tóth-Pál

#### Mail

Soby Mathew <soby.mathew@arm.com>

#### GitHub ID

soby-mathew

# 1.3 Change-log and Release notes

#### 1.3.1 v0.4.0

The following sections have the details on the release. This release has been verified with TF-A v2.10 release.

### New features in this release

- Added initial partial support for analysing RMM source code with CBMC (https://www.cprover.org/cbmc/).

- A new HOST\_VARIANT, *host\_cbmc*, has been introduced for this purpose.

- The CBMC testbench files and autogenerated files from RMM machine readable specification are imported into the source tree.

- An application note for the same is added to the documentation.

- Aligned the implementation to RMM v1.0 EAC5 specification.

- The relevant tag for the alignment is rmm-spec-v1.0-eac5.

- There is also an intermediate RMM v1.0 EAC2 alignment which is tagged rmm-spec-v1.0-eac2.

- Supported save and restore of Non Secure SME context when Realms are scheduled.

- The SIMD abstraction in RMM was reworked to cater for this requirement.

- Added support to emulate SME specific feature ID registers.

- Support injecting UNDEF exception into realm when SME is accessed within it.

- Also RMM now can handle SVE hint bit as specified by SMCCC v1.3 specification.

- Added TF-RMM Threat Model to the documentation.

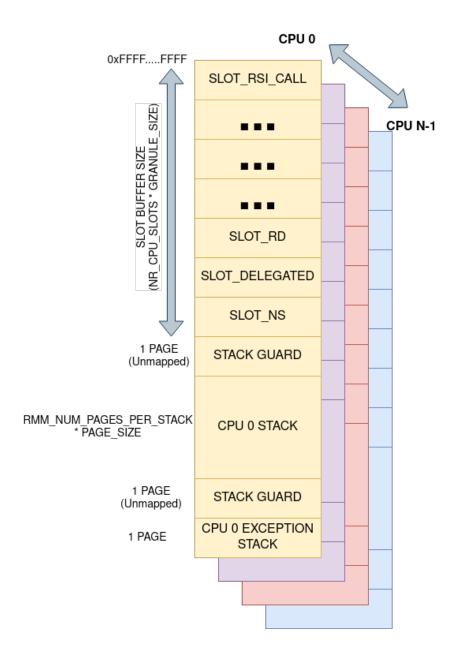

- Added capability to privately map the per-CPU stack.

- This contains any stack overflows to the particular CPU and prevents a CPU from corrupting another CPU stack.

- Added FEAT\_PAUTH and FEAT\_BTI support to RMM and also capability to use FEAT\_PAUTH within realms.

- Migrate to PSA Crypto API for attestation and measurement functionality in RMM.

- Added FEAT\_LPA2 support to Stage 1 MMU code (lib/xlat) in RMM.

- Added Stage 1 MMU setup design document.

### **Build/Testing/Tooling improvements**

- · Added static commit message checker which enforces the commit message guidelines mandated for the project.

- Added clang-tidy checker as one of the static analyzers.

- Several fixes to errors flagged by the static checker have been fixed.

- Fixed issues found in xlat lib unittests.

- Added github workflow for git submodules so that the TF-RMM dependencies display correctly in github.

- Added github workflow to configure an automatic message for PRs on GitHub and also build and run RMM unittests for every update of the *main* branch.

- Added FEAT\_LPA2 unit tests for lib/xlat module.

- Added RSI logger unit tests.

### **Platforms**

• The support for QEMU virt platform was merged.

#### Bug fixes/improvements in this release

- Fixed issue with TLB invalidations for unprotected mappings during RMI\_RTT\_DESTROY command.

- Fixed an issue wherein attest token write may return without releasing lock on the last level RTT of the mapped buffer.

- Enable TSW bit in hcr\_el2 when executing in Realm world so as to trap any data cache maintenance instructions that operate by Set/Way.

- Fixed issues flagged by coverity online scan. The defects detected can be found in the TF-RMM coverity scan online homepage.

- Fixed issues in s2tt management related to NS memory assignment/unassignment.

4 Chapter 1. About

- Added missing check to gicv3\_hcr field.

- Cache line align xlat lib data structures accessed by secondary CPUs to avoid data corruption due to mismatched memory attribute accesses by RMM during warm boot.

- Corrected linker options when building qcbor library.

- Fixes to comply with MISRA coding guidelines.

- Adjusted mbedTLS heap size depending on MAX\_CPUS in RMM.

- Fixed issue with RMI\_DATA\_CREATE\_UNKNOWN setting RIPAS to RAM.

- Added 'ipa\_bound' failure condition in RMI\_DATA\_DESTROY handler. Also added 'level\_bound' failure condition for RMI\_RTT\_MAP\_UNPROTECTED and RMI\_RTT\_UNMAP\_UNPROTECTED command handlers.

- Fixed issue with rsi\_log\_on\_exit() and modified the logging format.

- Fixed issue with change *ipa\_align* failure condition.

- Unified design of RSI/PSCI handlers.

- The issue with RMM config RMM\_FPU\_USE\_AT\_REL2 is fixed and the SIMD registers are saved and restored depending on the live register context in use which be one of FPU, SVE or SME.

- The compatibility check for RMM-EL3 interface version is hardened.

- Issue related to attestation token interruption flow is fixed.

- Enhanced the *fake\_host* sample application to do Realm token creation.

- Fixed D-cache maintenance in fvp\_set\_dram\_layout().

- Updated t\_cose submodule to use upstream version rather than a forked version.

#### Known issues and limitations

- Some capabilities as mentioned in RMM v1.0 EAC5 specification are restricted or absent in TF-RMM as listed below:

- The RMI\_RTT\_FOLD command only allows folding upto Level 2 even though the specification allows upto Level 1.

- The support for Self-hosted debug in Realms is not implemented.

- Although the RMM allows CCA attestation token sizes of larger than 4KB, there is a limitation on the size

of the Platform attestation token part. On the RMM-EL3 interface, there is only a shared buffer of 4KB

that is currently shared on the FVP. This needs to be enhanced so that larger platform token sizes can be

tested.

- The *rmm-el3-ifc* component does not always reset the RMM to the correct state on encountering an error. This needs to be corrected.

- The invocation of mmio\_emulation() and sea\_inj() functions need to be mutually exclusive during schedule of a REC. Currently both the cases are allowed to be satisfied at the same time which is incorrect.

### **Upcoming features**

- FEAT\_LPA2 support for Stage 2 MMU code (s2tt) in RMM.

- Add unit-tests for Stage 2 MMU code (s2tt) and also any associated rework for the s2tt component.

- Enhance CBMC analysis to more RMI commands.

- Fuzz testing for RMM utilizing the *fake\_host* architecture.

- Support for new capabilities like Device assignment as mandated by future versions of RMM specification.

- Integrate more static analyzers into RMM build system.

- Implement support for Self-hosted debug in realms.

#### 1.3.2 v0.3.0

The following sections have the details on the release. This release has been verified with TF-A v2.9 release.

#### New features in this release

- Add support to create Realms which can make use of SVE, if present in hardware.

- Refactor the Stage 1 translation table library *lib/xlat* API to better fit RMM usage. Also harden dynamic mapping via slot buffer mechanism by use of TRANSIENT software defined attribute.

- Add PMU support for Realms as described by RMM v1.0 Beta0 specification.

- Support getting DRAM info from the Boot manifest dynamically at runtime.

- RMM can now support the 2nd DDR bank on FVP.

#### **Build/Testing improvements**

- Define a unit test framework using CppUTest for RMM.

- Add unittests for *granule*, *slot-buffer* and Stage 1 translation table lib *xlat*.

- Improve the fake-host mock capability by adding support for per PE sysreg emulation.

- Improve the VA to PA mock layer for fake-host.

- Enable generation of gprof profiling data as part of fake-host runs.

- Improve the sample application on host-build platform by adding the cold attestation initialization flow. Also a sample minimal Realm create, run and destroy sequence is added to showcase the RMI calls involved.

- Further improvements to the unit test framework:

- Restore the sysreg state between test runs so each test gets a known sysreg state.

- Add capability to test assertions.

- Support dynamic behaviour for test harness depending on requirement.

- Add support for coverage report generation as part of unit test run.

- Build improvements in RMM:

- Move mbedTLS build from configure stage to build stage.

- Simplify QCBOR build.

6 Chapter 1. About

- Fix build artefact directory path to better cater to multi-config builds.

### Bug fixes in this release

- Remove HVC exit handling from RMI\_REC\_ENTER handler.

- Fix parameter in measurement extend sha512().

- Fix issues in *lib/xlat* for some corner cases.

- Mask MTE capability from id\_aa64pfr1\_el1 so that Realms can see that MTE is not supported.

- Add isb() after writes to cptr\_el2 system register.

- Fix the granule alignment check on granule\_addr.

- Fix some cppcheck warnings.

- Properly handle errors for granule (un)delegate calls.

- Fix the incorrect bit map manipulation for tracking VMID for realms.

- Fix some incorrect Block mapping cases in Stage 2 translation.

### **Upcoming features**

- RMM EAC Specification alignment.

- Support Self-Hosted Debug Realms.

- Support FEAT\_PAuth for Realms and utilize the same for RMM.

- Support LPA2 for Stage 2 Realm translation tables.

- Threat model covering RMM data flows.

- Enable Bounded Model Checker (CBMC) for source analysis.

- Save and restore SME/SME2 context belonging to NS Host. This allows NS Host to make use of SME/SME2 when Realms are scheduled.

### Known issues and limitations

- The size of RsiHostCall structure is 256 bytes in the implementation and aligns to RMM Beta1 specification rather than the 4 KB size specified in RMM Beta0 specification.

- The RMM Beta0 specification does not require to have a CBOR bytestream wrapper around the cca-platform-token and cca-realm-delegated-token, but the RMM implementation does so and this is aligned with later versions of the RMM specification (Beta2 onwards).

- The RMM config RMM\_FPU\_USE\_AT\_REL2 does not work as intended and this config is disabled by default. This will be fixed in a future release.

- When the RSI\_ATTEST\_TOKEN\_CONTINUE call is interrupted and then resumed later by Host via RMI\_REC\_ENTER, the original SMC is replayed again with the original arguments rather than returning RSI\_INCOMPLETE error code to Realm. The result is that the interrupted RSI call is continued again till completion and then returns back to Realm with the appropriate error code.

#### 1.3.3 v0.2.0

- This release has been verified with TF-A v2.8 release.

- The release has the following fixes and enhancements:

- Add support to render documentation on read-the-docs.

- Fix the known issue with RSI\_IPA\_STATE\_GET returning RSI\_ERROR\_INPUT for a destroyed IPA instead

of emulating data abort to NS Host.

- Fix an issue with RSI\_HOST\_CALL not returning back to Host to emulate a stage2 data abort.

- Harden an assertion check for do\_host\_call().

- The other known issues and limitations remain the same as listed for v0.1.0.

#### 1.3.4 v0.1.0

First TF-RMM source release aligned to RMM Beta0 specification. The specified interfaces: Realm Management Interface (RMI) and Realm Service Interface (RSI) are implemented which can attest and run Realm VMs as described by the Arm CCA Architecture.

### **Upcoming features**

- Support SVE, Self-Hosted Debug and PMU in Realms

- Support LPA2 for Stage 2 Realm translation tables.

- Threat model covering RMM data flows.

- Enable Bounded Model Checker (CBMC) for source analysis.

- Unit test framework based on RMM Fake host architecture.

#### Known issues and limitations

The following is a list of issues which are expected to be fixed in the future releases of TF-RMM:

- The size of RsiHostCall structure is 256 bytes in the implementation and aligns to RMM Beta1 specification rather than the 4 KB size specified in RMM Beta0 specification.

- The RSI\_IPA\_STATE\_GET command returns error RSI\_ERROR\_INPUT for a destroyed IPA instead of emulating data abort to Host.

- The RMM Beta0 specification does not require to have a CBOR bytestream wrapper around the cca-platform-token and cca-realm-delegated-token, but the RMM implementation does so.

8 Chapter 1. About

# 1.4 Developer Certificate of Origin

Developer Certificate of Origin Version 1.1

Copyright (C) 2004, 2006 The Linux Foundation and its contributors. 1 Letterman Drive Suite D4700 San Francisco, CA, 94129

Everyone is permitted to copy and distribute verbatim copies of this license document, but changing it is not allowed.

Developer's Certificate of Origin 1.1

By making a contribution to this project, I certify that:

- (a) The contribution was created in whole or in part by me and I have the right to submit it under the open source license indicated in the file; or

- (b) The contribution is based upon previous work that, to the best of my knowledge, is covered under an appropriate open source license and I have the right under that license to submit that work with modifications, whether created in whole or in part by me, under the same open source license (unless I am permitted to submit under a different license), as indicated in the file; or

- (c) The contribution was provided directly to me by some other person who certified (a), (b) or (c) and I have not modified it.

- (d) I understand and agree that this project and the contribution are public and that a record of the contribution (including all personal information I submit with it, including my sign-off) is maintained indefinitely and may be redistributed consistent with this project or the open source license(s) involved.

### 1.5 License

BSD 3-Clause License

Copyright TF-RMM Contributors All rights reserved.

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

10 Chapter 1. About

**CHAPTER**

**TWO**

# **GETTING STARTED GUIDES**

# 2.1 Prerequisite

This document describes the software requirements for building *RMM* for AArch64 target platforms.

It may possible to build *RMM* with combinations of software packages that are different from those listed below, however only the software described in this document can be officially supported.

### 2.2 Build Host

The *RMM* officially supports a limited set of build environments and setups. In this context, official support means that the environments listed below are actively used by team members and active developers, hence users should be able to recreate the same configurations by following the instructions described below. In case of problems, the *RMM* team provides support only for these environments, but building in other environments can still be possible.

We recommend at least Ubuntu 20.04 LTS (x64) for build environment. The arm64/AArch64 Ubuntu and other Linux distributions should also work fine, provided that the necessary tools and libraries can be installed.

# 2.3 Tool & Dependency overview

The following tools are required to obtain and build *RMM*:

| Name                   | Version             | Component                        |

|------------------------|---------------------|----------------------------------|

| C compiler             | see Setup Toolchain | Firmware                         |

| CMake                  | >=3.15.0            | Firmware, Documentation          |

| GNU Make               | >4.0                | Firmware, Documentation          |

| Python                 | 3.x                 | Firmware, Documentation          |

| Perl                   | >=5.26              | Firmware, Documentation          |

| ninja-build            |                     | Firmware (using Ninja Generator) |

| Sphinx                 | >=2.4,<3.0.0        | Documentation                    |

| sphinxcontrib-plantuml |                     | Documentation                    |

| sphinx-rtd-theme       |                     | Documentation                    |

| Git                    |                     | Firmware, Documentation          |

| Graphviz dot           | >v2.38.0            | Documentation                    |

| docutils               | >v2.38.0            | Documentation                    |

| gcovr                  | >=v4.2              | Tools(Coverage analysis)         |

| CBMC                   | >=5.84.0            | Tools(CBMC analysis)             |

| CPPcheck               | >=1.90              | Tools(CPPcheck)                  |

Table 1: Tool dependencies

# 2.4 Setup Toolchain

To compile *RMM* code for an AArch64 target, at least one of the supported AArch64 toolchains have to be available in the build environment.

Currently, the following compilers are supported:

- GCC (aarch64-none-elf-) >= 10.2-2020.11 (from the Arm Developer website)

- Clang+LLVM >= 14.0.0 (from the LLVM Releases website)

The respective compiler binary must be found in the shell's search path. Be sure to add the bin/ directory if you have downloaded a binary version. The toolchain to use can be set using RMM\_TOOLCHAIN parameter and can be set to either *llvm* or *gnu*. The default toolchain is *gnu*.

For non-native AArch64 target build, the CROSS\_COMPILE environment variable must contain the right target triplet corresponding to the AArch64 GCC compiler. Below is an example when RMM is to be built for AArch64 target on a non-native host machine and using GCC as the toolchain.

```

export CROSS_COMPILE=aarch64-none-elf-

export PATH=<path-to-aarch64-gcc>/bin:$PATH

```

Please note that AArch64 GCC must be included in the shell's search path even when using Clang as the compiler as LLVM does not include some C standard headers like *stdlib.h* and needs to be picked up from the *include* folder of the AArch64 GCC. Below is an example when RMM is to be built for AArch64 target on a non-native host machine and using LLVM as the toolchain.

```

export CROSS_COMPILE=aarch64-none-elf-

export PATH=<path-to-aarch64-gcc>/bin:<path-to-clang+llvm>/bin:$PATH

```

The CROSS\_COMPILE variable is ignored for fake\_host build and the native host toolchain is used for the build.

# 2.5 Package Installation (Ubuntu-20.04 x64)

If you are using the recommended Ubuntu distribution then we can install the required packages with the following commands:

1. Install dependencies:

sudo apt-get install -y git build-essential python3 python3-pip make ninja-build sudo snap install cmake

2. Verify cmake version:

```

cmake --version

```

**Note:** Please download cmake 3.19 or later version from https://cmake.org/download/.

3. Add CMake path into environment:

```

export PATH=<CMake path>/bin:$PATH

```

# 2.6 Install python dependencies

**Note:** The installation of Python dependencies is an optional step. This is required only if building documentation.

RMM's docs/requirements.txt file declares additional Python dependencies. Install them with pip3:

```

pip3 install --upgrade pip

cd <rmm source folder>

pip3 install -r docs/requirements.txt

```

# 2.7 Install coverage tools analysis dependencies

Note: This is an optional step only needed if you intend to run coverage analysis on the source code.

On Ubuntu, gcovr tool can be installed in two different ways:

Using the pagckage manager:

```

sudo apt-get install gcovr

```

The second (and recommended) way is install it with pip3:

```

pip3 install --upgrade pip

pip3 install gcovr

```

# 2.8 Getting the RMM Source

Source code for *RMM* is maintained in a Git repository hosted on TrustedFirmware.org. To clone this repository from the server, run the following in your shell:

```

git clone --recursive https://git.trustedfirmware.org/TF-RMM/tf-rmm.git

```

# 2.8.1 Additional steps for Contributors

If you are planning on contributing back to RMM, your commits need to include a Change-Id footer as explained in *Mandated Trailers*. This footer is generated by a Git hook that needs to be installed inside your cloned RMM source folder.

The TF-RMM Gerrit page under trustedfirmware.org contains a *Clone with commit-msg hook* subsection under its **Download** header where you can copy the command to clone the repo with the required git hooks. Please use the **SSH** option to clone the repository on your local machine.

If needed, you can also manually install the hooks separately on an existing repo:

```

curl -Lo $(git rev-parse --git-dir)/hooks/commit-msg https://review.trustedfirmware.org/

→tools/hooks/commit-msg

chmod +x $(git rev-parse --git-dir)/hooks/commit-msg

```

You can read more about Git hooks in the githooks page of the Git hooks documentation.

# 2.9 Install Cppcheck and dependencies

**Note:** The installation of Cppcheck is an optional step. This is required only if using the Cppcheck static analysis.

Follow the public documentation to install Cppcheck either from the official website https://cppcheck.sourceforge.io/or from the official github https://github.com/danmar/cppcheck/

If you own a valid copy of a MISRA rules file:

```

cp -a <path to the misra rules file>/<file name> ${RMM_SOURCE_DIR}/tools/cppcheck/misra.

_rules

```

### 2.10 Install CBMC

**Note:** The installation of CBMC is an optional step. This is required only if running source code analysis with CBMC.

Follow the public documentation to install CBMC either from the official website https://www.cprover.org/cbmc/ or from the official github https://github.com/diffblue/cbmc

# 2.11 Performing an Initial Build

The RMM sources can be compiled using multiple CMake options.

For detailed instructions on build configurations and examples see RMM Build Examples.

A typical build command for the FVP platform using GCC toolchain is shown below:

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR}

```

# 2.12 Running the RMM

The *RMM* is part of the CCA software stack and relies on EL3 Firmware to load the binary at boot time appropriately. It needs both EL3 Firmware and Non-Secure Host to be present at runtime for its functionality. The EL3 Firmware must comply to RMM-EL3 Communication Specification and is typically the TF-A. The Non-Secure Host can be an RME aware hypervisor or an appropriate Test utility running in Non-Secure world which can interact with *RMM* via Realm Management Interface (RMI).

The TF-A project includes build and run instructions for an RME enabled system on the FVP platform as part of TF-A RME documentation. The rmm.img binary is provided to the TF-A bootloader to be packaged in FIP using RMM build option in TF-A.

If *RMM* is built for the *fake\_host* architecture (see *RMM Fake Host Build*), then the generated *rmm.elf* binary can run natively on the Host machine. It does this by emulating parts of the system as described in *RMM Fake host architecture* design.

# 2.13 RMM Build Examples

The *RMM* supports a wide range of build configuration options. Some of these options are more regularly exercised by developers, while others are for **advanced** and **experimental** usage only.

*RMM* can be built using either GNU(GCC) or *LLVM(Clang)* toolchain. See *this section* for toolchain setup and the supported versions.

The build is performed in 2 stages:

**Configure Stage:** In this stage, a default config file can be specified which configures a sane config for the chosen platform. If this default config needs to be modified, it is recommended to first perform a default config and then modify using the cmake neurses as shown in *CMake UI Example*.

**Build Stage:** In this stage, the source build is performed by specifying the *-build* option. See any of the commands below for an example.

Note: It is recommended to clean build if any of the build options are changed from previous build.

Below are some of the typical build and configuration examples frequently used in *RMM* development for the FVP Platform. Detailed configuration options are described *here*.

RMM also supports a fake\_host build which can be used to build RMM for test and code analysis on the host machine. See *this section here* for more details.

1. Perform an initial default build with minimum configuration options:

Build using gnu toolchain

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR}

```

Build using LLVM toolchain

2. Perform an initial default config, then modify using ccmake ncurses UI:

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

ccmake -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR}

```

3. Perform a debug build and specify a log level:

4. Perform a documentation build:

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR} -DRMM_DOCS=ON

cmake --build ${RMM_BUILD_DIR} -- docs

```

5. Perform a clean verbose build:

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} --clean-first --verbose

```

6. Perform a build with Ninja Genenerator:

7. Perform a build with Ninja Multi Config Genenerator:

8. Perform a Cppcheck static analysis:

```

cmake -DRMM_CONFIG=fvp_defcfg -DCMAKE_EXPORT_COMPILE_COMMANDS=ON -S ${RMM_SOURCE_DIR} -B

$\times ${RMM_BUILD_DIR}$

cmake --build ${RMM_BUILD_DIR} -- cppcheck

cat ${BUILD_DIR}/tools/cppcheck/cppcheck.xml

```

9. Perform a Cppcheck static analysis with MISRA:

10. Perform a checkpatch analysis:

Run checkpatch on commits in the current branch against BASE\_COMMIT (default origin/master):

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} -- checkpatch

```

Run checkpatch on entire codebase:

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} -- checkcodebase

```

11. Perform a checkspdx analysis:

Run checkspdx on commits in the current branch against BASE\_COMMIT (default origin/master):

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} -- checkspdx-patch

```

Run checkspdx on entire codebase:

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} -- checkspdx-codebase

```

13. Check header file include order:

Run checkincludes-patch on commits in the current branch against BASE\_COMMIT (default origin/master):

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} -- checkincludes-patch

```

Run checkincludes on entire codebase:

```

cmake -DRMM_CONFIG=fvp_defcfg -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} -- checkincludes-codebase

```

14. Perform a clang-tidy analysis:

Run clang-tidy on commits in the current branch against BASE\_COMMIT (default origin/master):

```

cmake -DRMM_CONFIG=fvp_defcfg -DRMM_TOOLCHAIN=11vm -DCMAKE_EXPORT_COMPILE_COMMANDS=ON -S

-$\{RMM_SOURCE_DIR}\} -B $\{RMM_BUILD_DIR}\}

cmake --build $\{RMM_BUILD_DIR}\} -- clang-tidy-patch

```

Run clang-tidy on entire codebase:

```

cmake -DRMM_CONFIG=fvp_defcfg -DRMM_TOOLCHAIN=llvm -DCMAKE_EXPORT_COMPILE_COMMANDS=ON -S

$\instrum \$ \{\text{RMM_SOURCE_DIR}\} -\text{BUILD_DIR}\}$

cmake --build \$ \{\text{RMM_BUILD_DIR}\} -- \class \text{clang-tidy-codebase}

```

Note that clang-tidy will work with all configurations. It will only check the source files that are used for the specified configuration.

#### 15. Perform unit tests on development host:

Build and run unit tests on host platform. It is recommended to enable the Debug build of RMM.

Run unittests for a specific test group(s) (e.g. unittests whose group starts with 'xlat')

#### 16. Generate Coverage Report.

It is possible to generate a coverage report for a last execution of the host platform (whichever the variant) by using the *run-coverage* build target.

For example, to generate coverate report on the whole set of unittests:

```

cmake -DRMM_CONFIG=host_defcfg -DHOST_VARIANT=host_test -DRMM_COVERAGE=ON -DCMAKE_BUILD_

TYPE=Debug -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} -- run-unittests

cmake --build ${RMM_BUILD_DIR} -- run-coverage

```

Run coverage analysis on a specific set of unittests (e.g. unittests whose group starts with 'xlat')

Run coverage analysis on the *host\_build* variant of host platform:

```

cmake -DRMM_CONFIG=host_defcfg -DHOST_VARIANT=host_build -DRMM_COVERAGE=ON -DCMAKE_BUILD_

TYPE=Debug -S ${RMM_SOURCE_DIR} -B ${RMM_BUILD_DIR}

${RMM_BUILD_DIR}/Debug/rmm.elf

cmake --build ${RMM_BUILD_DIR} -- run-coverage

```

The above commands will automatically generate the HTML coverage report in folder *build/Debug/coverage* within the build directory. The HTML generation can be disabled by setting *RMM\_HTML\_COV\_REPORT=OFF*.

### 17. Run CBMC analysis:

Run COVERAGE, ANALYSIS and ASSERT targets for CBMC. The results are generated in \${RMM\_BUILD\_DIR}/tools/cbmc\_coverage\_results.

```

cmake -DRMM_CONFIG=host_defcfg -DHOST_VARIANT=host_cbmc -S ${RMM_SOURCE_DIR} -B ${RMM_

→BUILD_DIR}

cmake --build ${RMM_BUILD_DIR} -- cbmc-coverage cbmc-analysis cbmc-assert

```

# 2.14 RMM Build Options

The *RMM* build system supports the following CMake build options.

Table 2: RMM CMake Options Table

| Option             | Valid values                             | Default                       | Description                                                                   |

|--------------------|------------------------------------------|-------------------------------|-------------------------------------------------------------------------------|

| RMM_CONFIG         |                                          |                               | Platform build configuration, eg: fvp_defcfg for the FVP                      |

| RMM_ARCH           | aarch64   fake_host                      | aarch64                       | Target Architecture for RMM build                                             |

| RMM_MAX_SIZE       |                                          | 0x0                           | Maximum size for RMM image                                                    |

| MAX_CPUS           |                                          | 16                            | Maximum number of CPUs supported by RMM                                       |

| GRANULE_SHIFT      |                                          | 12                            | Granule Shift used by RMM                                                     |

| RMM_CCA_TOKEN_BU   | JFFER                                    | 1                             | Number of pages to allocate in Aux granules for Realm CCA token               |

| RMM_DOCS           | ON   OFF                                 | OFF                           | RMM Documentation build                                                       |

| CMAKE_BUILD_TYPE   |                                          | Release                       | CMake Build type                                                              |

| CMAKE_CONFIGURAT   |                                          | Debug & Release               | Multi-generator configuration types                                           |

| CMAKE_DEFAULT_BU   |                                          | Release                       | Default multi-generator configuration type                                    |

| MbedTLS_BUILD_TYPI |                                          | Release                       | MbedTLS build type                                                            |

| RMM_PLATFORM       | fvp   host                               |                               | Platform to build                                                             |

| RMM_TOOLCHAIN      | gnu   llvm                               |                               | Toolchain name                                                                |

| LOG_LEVEL          | 0 - 50                                   | 40(Debug)<br>20(Release)      | Log level to apply for RMM (0 - 50).                                          |

| RMM_STATIC_ANALYS  | SIS                                      |                               | Enable static analysis checkers                                               |

| RMM_UART_ADDR      |                                          | 0x0                           | Base addr of UART to be used for RMM logs                                     |

| PLAT_CMN_CTX_MAX   |                                          | 0                             | Maximum number of translation tables used by the runtime context              |

| PLAT_CMN_EXTRA_M   | MAP_REGIONS                              | 0                             | Extra platform mmap regions that need to be mapped in S1 xlat tables          |

| RMM_NUM_PAGES_PE   | R_STACK                                  | 5                             | Number of pages to use per CPU stack                                          |

| MBEDTLS_ECP_MAX_   | O <b>124</b> 88 -                        | 1000                          | Number of max operations per ECC signing iteration                            |

| RMM_FPU_USE_AT_RI  | ELOZN   OFF                              | OFF(fake_host)<br>ON(aarch64) | Enable FPU/SIMD usage in RMM.                                                 |

| RMM_MAX_GRANULE    | ES                                       | 0                             | Maximum number of memory granules available to the system                     |

| HOST_VARIANT       | host_build<br>  host_test  <br>host_cbmc | host_build                    | Variant to build for the host platform. Only available when RMM_PLATFORM=host |

| HOST_MEM_SIZE      |                                          | 0x40000000                    | Host memory size that will be used as physical granules                       |

| RMM_COVERAGE       | ON   OFF                                 | OFF                           | Enable coverage analysis                                                      |

| RMM_HTML_COV_REI   | POORT   OFF                              | ON                            | Enable HTML output report for coverage analysis                               |

| RMM_CBMC_VIEWER    | _ONTPOHF                                 | OFF                           | Generate report of CBMC results using the tool cbmc-viewer                    |

| RMM_CBMC_SINGLE_   | TESTBENCH                                | OFF                           | Run CBMC on a single testbench instead on all of them                         |

# 2.15 RMM LLVM Build

RMM can be built using LLVM Toolchain (Clang). To build using LLVM toolchain, set RMM\_TOOLCHAIN=llvm during configuration stage.

# 2.16 RMM Fake Host Build

RMM also provides a fake\_host target architecture which allows the code to be built natively on the host using the host toolchain. To build for fake\_host architecture, set RMM\_CONFIG=host\_defcfg during the configuration stage.

**CHAPTER**

THREE

### **PROCESS**

# 3.1 Coding Standard

This document describes the coding rules to follow to contribute to the project.

### 3.1.1 General

The following coding standard is derived from MISRA C:2012 Guidelines, TF-A coding style and Linux kernel coding style coding standards.

### 3.1.2 File Encoding

The source code must use the **UTF-8** character encoding. Comments and documentation may use non-ASCII characters when required (e.g. Greek letters used for units) but code itself is still limited to ASCII characters.

### 3.1.3 Language

The primary language for comments and naming must be International English. In cases where there is a conflict between the American English and British English spellings of a word, the American English spelling is used.

Exceptions are made when referring directly to something that does not use international style, such as the name of a company. In these cases the existing name should be used as-is.

### 3.1.4 C Language Standard

The C language mode used for *RMM* is *GNU11*. This is the "GNU dialect of ISO C11", which implies the *ISO C11* standard with GNU extensions.

Both GCC and Clang compilers have support for *GNU11* mode, though Clang does lack support for a small number of GNU extensions. These missing extensions are rarely used, however, and should not pose a problem.

### 3.1.5 Length

• Each file, function and scopes should have a logical uniting theme.

No length limit is set for a file.

• A function should be 24 lines maximum.

This will not be enforced, any function being longer should trigger a discussion during the review process.

- The recommended maximum line length is 80 characters, except for string literals as it would make any search for it more difficult. A maximum length of 100 characters is enforced by the coding guidelines static check.

- A variable should not be longer than 31 characters.

Although the C11 specification specifies that the number of signitificant characters in an identifier is implementation defined it sets the translation limit to the 31 initial characters.

| TYPE       | LIMIT                   |

|------------|-------------------------|

| function   | 24 lines (not enforced) |

| line       | 100 characters          |

| identifier | 31 characters           |

### 3.1.6 Headers/Footers

• Include guards:

```

#ifndef FILE_NAME_H

#define FILE_NAME_H

<header content>

#endif /* FILE_NAME_H */

```

• Include statement variant is <>:

```

#include <file.h>

```

• Include files should be alphabetically ordered:

```

#include <axxxx.h>

#include <bxxxx.h>

[...]

#include <zxxxx.h>

```

• If possible, use forward declaration of struct types in public headers. This will reduce interdependence of header file inclusion.

```

#include <axxxx.h>

#include <bxxxx.h>

[...]

/* forward declaration */

struct x;

void foo(struct *x);

```

### 3.1.7 Naming conventions

• Case: Functions and variables must be in Snake Case

```

unsigned int my_snake_case_variable = OU;

void my_snake_case_function(void)

{

[...]

}

```

• Local variables should be declared at the top of the closest opening scope and should be short.

We won't enforce a length, and defining short is difficult, this motto (from Linux) catches the spirit

LOCAL variable names should be short, and to the point.

If you have some random integer loop counter, it should probably be called i.

Calling it loop\_counter is non-productive, if there is no chance of it being mis-understood.

Similarly, tmp can be just about any type of variable that is used to hold a temporary value.

If you are afraid to mix up your local variable names, you have another problem.

```

int foo(const int a)

{

int c; /* needed in the function */

c = a; /* MISRA-C rules recommend to not modify arguments variables */

if (c == 42) {

int b; /* needed only in this "if" statment */

b = bar(); /* bar will return an int */

if (b != -1) {

c += b;

}

}

return c;

}

```

• Use an appropriate prefix for public API of a component. For example, if the component name is *bar*, then the init API of the component should be called *bar\_init()*.

### 3.1.8 Indentation

Use **tabs** for indentation. The use of spaces for indentation is forbidden except in the case where a term is being indented to a boundary that cannot be achieved using tabs alone.

Tab spacing should be set to 8 characters.

Trailing whitespaces or tabulations are not allowed and must be trimmed.

# 3.1.9 Spacing

Single spacing should be used around most operators, including:

- Arithmetic operators (+, -, /, \*, %)

- Assignment operators (=, +=, etc)

- Boolean operators (&&, ||)

- Comparison operators (<, >, ==, etc)

- Shift operators (>>, <<)

- Logical operators (&, |, etc)

- Flow control (if, else, switch, while, return, etc)

No spacing should be used around the following operators

- Cast (())

- Indirection (\*)

### 3.1.10 Braces

- Use K&R style for statements.

- Function opening braces are on a new line.

- Use braces even for singled line.

### 3.1.11 Commenting

Double-slash style of comments (//) is not allowed, below are examples of correct commenting.

```

/*

* This example illustrates the first allowed style for multi-line comments.

*

* Blank lines within multi-lines are allowed when they add clarity or when

* they separate multiple contexts.

*/

```

```

/* Single line comments can use this format */

```

# 3.1.12 Error return values and Exception handling

- Function return type must be explicitly defined.

- Unless specified otherwise by an official specification, return values must be used to return success or failure (Standard Posix error codes).

### Return an integer if the function is an action or imperative command

Failure: -Exxx (STD posix error codes, unless specified otherwise)

Success: 0

#### Return a boolean if the function is as predicate

Failure: false Success: true

• If a function returns error information, then that error information shall be tested.

Exceptions are allowed for STDLIB functions (memcpy/printf/...) in which case it must be void casted.

```

#define MY_TRANSFORMED_ERROR (-1)

void my_print_function(struct my_struct in_mystruct)

{

long long transformed_a = my_transform_a(in_mystruct.a);

if (transform_a != MY_TRANSFORMED_ERROR) {

(void)printf("STRUCT\n\tfield(a): %11\n", transformed_a);

```

(continues on next page)

(continued from previous page)

```

} else {

(void)printf("STRUCT\n\tERROR %11\n", transformed_a);

}

```

### 3.1.13 Use of asserts and panic

Assertions, as a general rule, are only used to catch errors during development cycles and are removed from production binaries. They are useful to document pre-conditions for a function or impossible conditions in code. They are not substitutes for proper error checking and any expression used to test an assertion must not have a side-effect.

For example,

```

assert(--i == 0);

```

should not be used in code.

Assertions can be used to validate input arguments to an API as long as the caller and callee are within the same trust boundary.

panic() is used in places wherein it is not possible to continue the execution of program sensibly. It should be used sparingly within code and, if possible, instead of panic(), components should return error back to the caller and the caller can decide on the appropriate action. This is particularly useful to build resilence to the program wherein nonfunctional part of the program can be disabled and, if possible, other functional aspects of the program can be kept running.

# 3.1.14 Using COMPILER\_ASSERT to check for compile time data errors

Where possible, use the COMPILER\_ASSERT macro to check the validity of data known at compile time instead of checking validity at runtime, to avoid unnecessary runtime code.

For example, this can be used to check that the assembler's and compiler's views of the size of an array is the same.

```

#include <utils_def.h>

define MY_STRUCT_SIZE 8 /* Used by assembler source files */

struct my_struct {

uint32_t arg1;

uint32_t arg2;

};

COMPILER_ASSERT(MY_STRUCT_SIZE == sizeof(struct my_struct));

```

If MY\_STRUCT\_SIZE in the above example were wrong then the compiler would emit an error like this:

# 3.1.15 Data types, structures and typedefs

• Data Types:

The *RMM* codebase should be kept as portable as possible for 64-bits platforms. To help with this, the following data type usage guidelines should be followed:

- Where possible, use the built-in *C* data types for variable storage (for example, char, int, long long, etc) instead of the standard *C11* types. Most code is typically only concerned with the minimum size of the data stored, which the built-in *C* types guarantee.

- Avoid using the exact-size standard C11 types in general (for example, uint16\_t, uint32\_t, uint64\_t, etc) since they can prevent the compiler from making optimizations. There are legitimate uses for them, for example to represent data of a known structure. When using them in a structure definition, consider how padding in the structure will work across architectures.

- Use int as the default integer type it's likely to be the fastest on all systems. Also this can be assumed to be 32-bit as a consequence of the Procedure Call Standard for the Arm 64-bit Architecture.

- Avoid use of short as this may end up being slower than int in some systems. If a variable must be exactly 16-bit, use int16\_t or uint16\_t.

- long are defined as LP64 (64-bit), this is guaranteed to be 64-bit.

- Use char for storing text. Use uint8\_t for storing other 8-bit data.

- Use unsigned for integers that can never be negative (counts, indices, sizes, etc). *RMM* intends to comply with MISRA "essential type" coding rules (10.X), where signed and unsigned types are considered different essential types. Choosing the correct type will aid this. MISRA static analysers will pick up any implicit signed/unsigned conversions that may lead to unexpected behaviour.

- For pointer types:

- If an argument in a function declaration is pointing to a known type then simply use a pointer to that type (for example: struct my\_struct \*).

- If a variable (including an argument in a function declaration) is pointing to a general, memory-mapped address, an array of pointers or another structure that is likely to require pointer arithmetic then use uintptr\_t. This will reduce the amount of casting required in the code. Avoid using unsigned long or unsigned long for this purpose; it may work but is less portable.

- Use of void \* is generally discouraged. Although it is useful to represent pointers to types that are abstracted away from the callers and has useful implicit cast properties, for the sake of a more uniform code base, we encourage use of uintptr\_t where possible.

- Avoid pointer arithmetic generally (as this violates MISRA C 2012 rule 18.4) and especially on void pointers

(as this is only supported via language extensions and is considered non-standard). In *RMM*, setting the

W build flag to W=3 enables the -Wpointer-arith compiler flag and this will emit warnings where pointer

arithmetic is used.

- Use ptrdiff\_t to compare the difference between 2 pointers.

- Use size\_t when storing the sizeof() something.

- Use ssize\_t when returning the sizeof() something from a function that can also return an error code; the signed type allows for a negative return code in case of error. This practice should be used sparingly.

- Use uint64\_t to store the contents of an AArch64 register or represent a 64-bit value. Use of unsigned long or u\_register\_t for these purposes is discouraged.

These guidelines should be updated if additional types are needed.

• Typedefs:

Typedef should be avoided and used only to create opaque types. An opaque data type is one whose concrete data structure is not publicly defined. Opaque data types can be used on handles to resources that the caller is not expected to address directly.

```

/* File my_lib.h */

#ifndef MY_LIB_H

#define MY_LIB_H

typedef struct my_lib_context {

[...] /* whatever internal private variables you need in my_lib */

} context_t;

#endif /* MY_LIB_H */

```

### 3.1.16 Macros and Enums

- Favor functions over macros.

- Preprocessor macros and enums values are written in all uppercase text.

- A numerical value shall be typed.

```

/* Common C usage */

#define MY_MACRO 4UL

/* If used in C and ASM (included from a .S file) */

#define MY_MACRO UL(4)

```

- Expressions resulting from the expansion of macro parameters must be enclosed in parentheses.

- A macro parameter immediately following a # operator mustn't be immediately followed by a ## operator.

• Avoid defining macros that affect the control flow (i.e. avoid using return/goto in a macro).

• Macro with multiple statements can be enclosed in a do-while block or in a expression statement.

```

int foo(char **b);

#define M1(a, b)

do {

if((a) == 5) {

foo((b));

} while (false)

#define M2(a, b)

({

if ((a) == 5) {

foo((b));

}

})

int foo(char **b)

return 42;

}

int main(int ac, char **av)

{

if (ac == 1) {

M1(ac, av);

} else if (ac == 2) {

M2(ac, av);

} else {

return -1;

return ac;

}

```

### 3.1.17 Switch statements

- Return in a *case* are allowed.

- Fallthrough are allowed as long as they are commented.

- Do not rely on type promotion between the switch type and the case type.

### 3.1.18 Inline assembly

- Favor C language over assembly language.

- Document all usage of assembly.

- Do not mix C and ASM in the same file.

### 3.1.19 Libc functions that are banned or to be used with caution

Below is a list of functions that present security risks.

| libc function            | Comments                                                              |

|--------------------------|-----------------------------------------------------------------------|

| strcpy, wcscpy, strncpy  | use strlcpy instead                                                   |

| strcat, wcscat, strncat  | use strlcat instead                                                   |

| sprintf, vsprintf        | use snprintf, vsnprintf instead                                       |

| snprintf                 | if used, ensure result fits in buffer i.e : snprintf(buf,size) < size |

| vsnprintf                | if used, inspect va_list match types specified in format string       |

| strtok, strtok_r, strsep | Should not be used                                                    |

| ato*                     | Should not be used                                                    |

| *toa                     | Should not be used                                                    |

The use of above functions are discouraged and will only be allowed in justified cases after a discussion has been held either on the mailing list or during patch review and it is agreed that no alternative to their use is available. The code containing the banned APIs must properly justify their usage in the comments.

The above restriction does not apply to Third Party IP code inside the ext/ directory.

# 3.2 Security Handling

The generic security incident process can be found at TrustedFirmware.org security incident process.

# 3.3 Commit Style

When writing commit messages, please think carefully about the purpose and scope of the change you are making: describe briefly what the change does, and describe in detail why it does it. This helps to ensure that changes to the code-base are transparent and approachable to reviewers, and it allows us to keep a more accurate changelog. You may use Markdown in commit messages.

A good commit message provides all the background information needed for reviewers to understand the intent and rationale of the patch. This information is also useful for future reference. For example:

- What does the patch do?

- · What motivated it?

- What impact does it have?

- How was it tested?

- Have alternatives been considered? Why did you choose this approach over another one?

- If it fixes an issue, include a reference.

- Github prescribes a format for issue fixes that can be used within the commit message:

```

Fixes TF-RMM/tf-rmm#<issue-number>

```

Commit messages are expected to be of the following form, based on conventional commits:

```

<type>[optional scope]: <description>

[optional body]

[optional trailer(s)]

```

The following *types* are permissible :

| Type     | Description                                                                                       |

|----------|---------------------------------------------------------------------------------------------------|

| feat     | A new feature                                                                                     |

| fix      | A bug fix                                                                                         |

| build    | Changes that affect the build system or external dependencies                                     |

| docs     | Documentation-only changes                                                                        |

| perf     | A code change that improves performance                                                           |

| refactor | A code change that neither fixes a bug nor adds a feature                                         |

| revert   | Changes that revert a previous change                                                             |

| style    | Changes that do not affect the meaning of the code (white-space, formatting, missing semi-colons, |

|          | etc.)                                                                                             |

| test     | Adding missing tests or correcting existing tests                                                 |

| chore    | Any other change                                                                                  |

The permissible *scopes* are more flexible, and we recommend that they match the directory where the patch applies (or where the main subject of the patch is, in case of changes accross several directories).

The following example commit message demonstrates the use of the refactor type and the lib/arch scope:

```

refactor(lib/arch): ...

This change introduces ....

Change-Id: ...

Signed-off-by: ...

```

In addition, the width of the commit message must be no more than 72 characters.

### 3.3.1 Mandated Trailers

Commits are expected to be signed off with the Signed-off-by: trailer using your real name and email address. You can do this automatically by committing with Git's -s flag.

There may be multiple Signed-off-by: lines depending on the history of the patch. See *License and Copyright for Contributions* for guidance on this.

Ensure that each commit also has a unique Change-Id: line. If you have cloned the repository using the "Clone with commit-msg hook" clone method, then this should be done automatically for you.

More details may be found in the Gerrit Change-Ids documentation.

3.3. Commit Style 31

### 3.4 Contributor's Guide

# 3.4.1 Getting Started

- Make sure you have a Github account and you are logged on review.trustedfirmware.org.

- Clone RMM on your own machine as described in Getting the RMM Source.

- If you plan to contribute a major piece of work, it is usually a good idea to start a discussion around it on the mailing list. This gives everyone visibility of what is coming up, you might learn that somebody else is already working on something similar or the community might be able to provide some early input to help shaping the design of the feature.

- If you intend to include Third Party IP in your contribution, please mention it explicitly in the email thread and ensure that the changes that include Third Party IP are made in a separate patch (or patch series).

- Create a local topic branch based on the RMM main branch.

# 3.4.2 Making Changes

- See the License and Copyright for Contributions section for guidance on license and copyright.

- Ensure commits adhere to the project's Commit Style.

- Make commits of logical units. See these general Git guidelines for contributing to a project.

- Keep the commits on topic. If you need to fix another bug or make another enhancement, please address it on a separate topic branch.

- Split the patch into manageable units. Small patches are usually easier to review so this will speed up the review process.

- Avoid long commit series. If you do have a long series, consider whether some commits should be squashed together or addressed in a separate topic.

- Follow the *Coding Standard*.

- Use the static checks as shown in RMM Build Examples to perform checks like checkpatch, checkspdx, header files include order etc.

- Where appropriate, please update the documentation.

- Consider whether the *Design* document or other in-source documentation needs updating.

- Ensure that each patch in the patch series compiles in all supported configurations. For generic changes, such as on the libraries, The *RMM Fake host architecture* should be able to, at least, build. Patches which do not compile will not be merged.

- Please test your changes and add suitable tests in the available test frameworks for any new functionality.

- Ensure that all CI automated tests pass. Failures should be fixed. They might block a patch, depending on how critical they are.

# 3.4.3 Submitting Changes

• Assuming the clone of the repo has been done as mentioned in the *Getting the RMM Source* and *origin* refers to the upstream repo, submit your changes for review targeting the integration branch. Create a topic that describes the target of your changes to help group related patches together.

```

git push origin HEAD:refs/for/integration [-o topic=<your_topic>]

```

Refer to the Gerrit Uploading Changes documentation for more details.

- Add reviewers for your patch:

- At least one maintainer. See the list of *Maintainers*.

- Alternatively, you might send an email to the TF-RMM mailing list to broadcast your review request to the community.

- The changes will then undergo further review by the designated people. Any review comments will be made directly on your patch. This may require you to do some rework. For controversial changes, the discussion might be moved to the TF-RMM mailing list to involve more of the community.

- The patch submission rules are the following. For a patch to be approved and merged in the tree, it must get a Code-Review+2.

In addition to that, the patch must also get a Verified+1. This is usually set by the Continuous Integration (CI) bot when all automated tests passed on the patch. Sometimes, some of these automated tests may fail for reasons unrelated to the patch. In this case, the maintainers might (after analysis of the failures) override the CI bot score to certify that the patch has been correctly tested.

In the event where the CI system lacks proper tests for a patch, the patch author or a reviewer might agree to perform additional manual tests in their review and the reviewer incorporates the review of the additional testing in the Code-Review+1 to attest that the patch works as expected.

- When the changes are accepted, the *Maintainers* will integrate them.

- Typically, the *Maintainers* will merge the changes into the integration branch.

- If the changes are not based on a sufficiently-recent commit, or if they cannot be automatically rebased, then the *Maintainers* may rebase it on the integration branch or ask you to do so.

- After final integration testing, the changes will make their way into the main branch. If a problem is found during integration, the *Maintainers* will request your help to solve the issue. They may revert your patches and ask you to resubmit a reworked version of them or they may ask you to provide a fix-up patch.

# 3.4.4 License and Copyright for Contributions

All new files should include the BSD-3-Clause SPDX license identifier where possible. When contributing code to us, the committer and all authors are required to make the submission under the terms of the *Developer Certificate of Origin*, confirming that the code submitted can (legally) become part of the project, and be subject to the same BSD-3-Clause license. This is done by including the standard Git Signed-off-by: line in every commit message. If more than one person contributed to the commit, they should also add their own Signed-off-by: line.

Files that entirely consist of contributions to this project should have a copyright notice and BSD-3-Clause SPDX license identifier of the form :

```

SPDX-License-Identifier: BSD-3-Clause

SPDX-FileCopyrightText: Copyright TF-RMM Contributors.

```

# **Realm Management Monitor**

Patches that contain changes to imported Third Party IP files should retain their original copyright and license notices. If changes are made to the imported files, then add an additional SPDX-FileCopyrightText tag line as shown above.

34 Chapter 3. Process

**CHAPTER**

**FOUR**

# DESIGN

# 4.1 RMM Locking Guidelines

This document outlines the locking requirements, discusses the implementation and provides guidelines for a deadlock free *RMM* implementation. Further, the document hitherto is based upon *RMM* Alpha-05 specification and is expected to change as the implementation proceeds.

## 4.1.1 Introduction

In order to meet the requirement for the *RMM* to be small, simple to reason about, and to co-exist with contemporary hypervisors which are already designed to manage system memory, the *RMM* does not include a memory allocator. It instead relies on an untrusted caller providing granules of memory used to hold both meta data to manage realms as well as code and data for realms.

To maintain confidentiality and integrity of these granules, the *RMM* implements memory access controls by maintaining awareness of the state of each granule (aka Granule State, ref *Implementation*) and enforcing rules on how memory granules can transition from one state to another and how a granule can be used depending on its state. For example, all granules that can be accessed by software outside the *PAR* of a realm are in a specific state, and a granule that holds meta data for a realm is in another specific state that prevents it from being used as data in a realm and accidentally corrupted by a realm, which could lead to internal failure in the *RMM*.

Due to this complex nature of the operations supported by the *RMM*, for example when managing page tables for realms, the *RMM* must be able to hold locks on multiple objects at the same time. It is a well known fact that holding multiple locks at the same time can easily lead to deadlocking the system, as for example illustrated by the dining philosophers problem [EWD310]. In traditional operating systems software such issues are avoided by defining a partial order on all system objects and always acquiring a lower-ordered object before a higher-ordered object. This solution was shown to be correct by Dijkstra [EWD625]. Solutions are typically obtained by assigning an arbitrary order based upon certain attributes of the objects, for example by using the memory address of the object.

Unfortunately, software such as the *RMM* cannot use these methods directly because the *RMM* receives an opaque pointer from the untrusted caller and it cannot know before locking the object if it is indeed of the expected state. Furthermore, MMU page tables are hierarchical data structures and operations on the page tables typically must be able to locate a leaf node in the hierarchy based on single value (a virtual address) and therefore must walk the page tables in their hierarchical order. This implies an order of objects in the same Granule State which is not known by a process executing in the *RMM* before holding at least one lock on object in the page table hierarchy. An obvious solution to these problems would be to use a single global lock for the *RMM*, but that would serialize all operations across all shared data structures in the system and severely impact performance.

## 4.1.2 Requirements

To address the synchronization needs of the *RMM* described above, we must employ locking and lock-free mechanisms which satisfies a number of properties. These are discussed below:

#### **Critical Section**

A critical section can be defined as a section of code within a process that requires access to shared resources and that must not be executed while another process is in a corresponding section of code [WS2001].

Further, access to shared resources without appropriate synchronization can lead to **race conditions**, which can be defined as a situation in which multiple threads or processes read and write a shared item and the final result depends on the relative timing of their execution [WS2001].

In terms of *RMM*, an access to a shared resource can be considered as a list of operations/instructions in program order that either reads from or writes to a shared memory location (e.g. the granule data structure or the memory granule described by the granule data structure, ref *Implementation*). It is also understood that this list of operations does not execute indefinitely, but eventually terminates.

We can now define our desired properties as follows:

#### **Mutual Exclusion**

Mutual exclusion can be defined as the requirement that when one process is in a critical section that accesses shared resources, no other process may be in a critical section that accesses any of those shared resources [WS2001].

The following example illustrates how an implementation might enforce mutual exclusion of critical sections using a lock on a valid granule data structure *struct granule* \*a:

```

struct granule *a;

bool r;

r = try_lock(a);

if (!r) {

return -ERROR;

}

critical_section(a);

unlock(a);

other_work();

```

We note that a process might fail to perform the lock operation on object a and return an error or successfully acquire the lock, execute the  $critical\ section()$ , unlock() and then continue to make forward progress to  $other\ work()$  function.

#### **Deadlock Avoidance**

A deadlock can be defined as a situation in which two or more processes are unable to proceed because each is waiting for one of the others to do something [WS2001].

In other words, one or more processes are trying to enter their critical sections but none of them make forward progress.

We can then define the deadlock avoidance property as the inverse scenario:

When one or more processes are trying to enter their critical sections, at least one of them makes forward progress.

A deadlock is a fatal event if it occurs in supervisory software such as the *RMM*. This must be avoided as it can render the system vulnerable to exploits and/or unresponsive which may lead to data loss, interrupted service and eventually economic loss.

#### **Starvation Avoidance**

Starvation can be defined as a situation in which a runnable process is overlooked indefinitely by the scheduler; although it is able to proceed, it is never chosen [WS2001].

Then starvation avoidance can be defined as, all processes that are trying to enter their critical sections eventually make forward progress.

Starvation must be avoided, because if one or more processes do not make forward progress, the PE on which the process runs will not perform useful work and will be lost to the user, resulting in similar issues like a deadlocked system.

#### **Nested Critical Sections**

A critical section for an object may be nested within the critical section for another object for the same process. In other words, a process may enter more than one critical section at the same time.

For example, if the *RMM* needs to copy data from one granule to another granule, and must be sure that both granules can only be modified by the process itself, it may be implemented in the following way:

```

struct granule *a;

struct granule *b;

bool r;

r = try_lock(a);

if (!r) {

return -ERROR;

}

/* critical section for granule a -- ENTER */

r = try_lock(b);

if (r) {

/* critical section for granule b -- ENTER */

b->foo = a->foo;

/* critical section for granule b -- EXIT */

unlock(b);

/* critical section for granule a -- EXIT */

unlock(a);

```

## 4.1.3 Implementation

The *RMM* maintains granule states by defining a data structure for each memory granule in the system. Conceptually, the data structure contains the following fields:

- · Granule State

- Lock

- Reference Count

The Lock field provides mutual exclusion of processes executing in their critical sections which may access the shared granule data structure and the shared meta data which may be stored in the memory granule which is in one of the *RD*, *REC*, and Table states. Both the data structure describing the memory granule and the contents of the memory granule itself can be accessed by multiple PEs concurrently and we therefore require some concurrency protocol to avoid corruption of shared data structures. An alternative to using a lock providing mutual exclusion would be to design all operations that access shared data structures as lock-free algorithms, but due to the complexity of the data structures and the operation of the *RMM* we consider this too difficult to accomplish in practice.

The Reference Count field is used to keep track of references between granules. For example, an *RD* describes a realm, and a *REC* describes an execution context within that realm, and therefore an *RD* must always exist when a *REC* exists. To prevent the *RMM* from destroying an *RD* while a *REC* still exists, the *RMM* holds a reference count on the *RD* for each *REC* associated with the same realm, and only when the all the RECs in a realm have been destroyed and the reference count on an *RD* drops to zero, can the *RD* be destroyed and the granule be repurposed for other use.

Based on the above, we now describe the Granule State field and the current locking/refcount implementation:

- **UnDelegated:** These are granules for which *RMM* does not prevent the *PAS* of the granule from being changed by another agent to any value. In this state, the granule content access is not protected by granule::lock, as it is always subject to reads and writes from Non-Realm worlds.